Cognichip’s $60M Series A sets a 12–18 month test: can its physics‑informed AI deliver production tapeouts?

Cognichip has closed a $60 million Series A and doubled down on a physics‑informed approach to automate chip design — but the company faces a clear, near-term test: show production tapeouts and independent validation within about 12–18 months.

Funding round and board moves that change the signal-to-noise

The Series A was led by Seligman Ventures and brings Cognichip’s total funding to $93 million since its 2024 founding. Intel CEO Lip‑Bu Tan and Umesh Padval of Seligman Ventures joined the company’s board, signaling heavyweight semiconductor industry support for Cognichip’s direction and giving the startup direct access to seasoned executive judgment about commercializing EDA‑adjacent tech.

Those appointments matter materially: Tan has led Cadence Design Systems in the past and now runs Intel, so his board seat is not just a logo — it connects Cognichip to maker and customer perspectives that will shape access to proprietary process node know‑how and foundry relationships that the company says it needs to prove manufacturability.

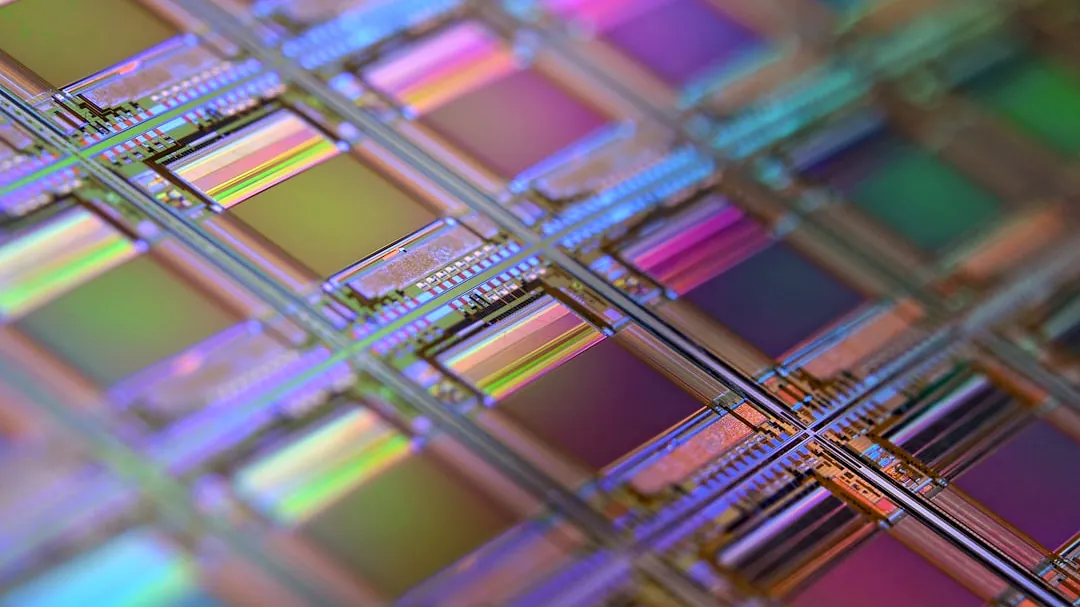

What “physics‑informed” means here, and why data governance is the bottleneck

Cognichip brands its stack Artificial Chip Intelligence (ACI®), built on foundation models trained on a mix of proprietary partner data, synthetic datasets, and physics‑aware modeling rather than generic LLMs. The firm positions that approach as necessary to respect circuit physics, timing closure, power distribution, and process variation constraints that simple language models cannot encode.

Practically, this requires two nontrivial capabilities: assembling deep, guarded chip‑level datasets and running secure, audited training so customers’ IP isn’t exposed. Cognichip says it has built synthetic data pipelines and license agreements plus tooling for in‑place model fine‑tuning on customer IP. Those governance mechanisms are the operational condition for any claim of “production‑ready” automation in EDA.

Customer engagements, demos, and the hard evidence gap

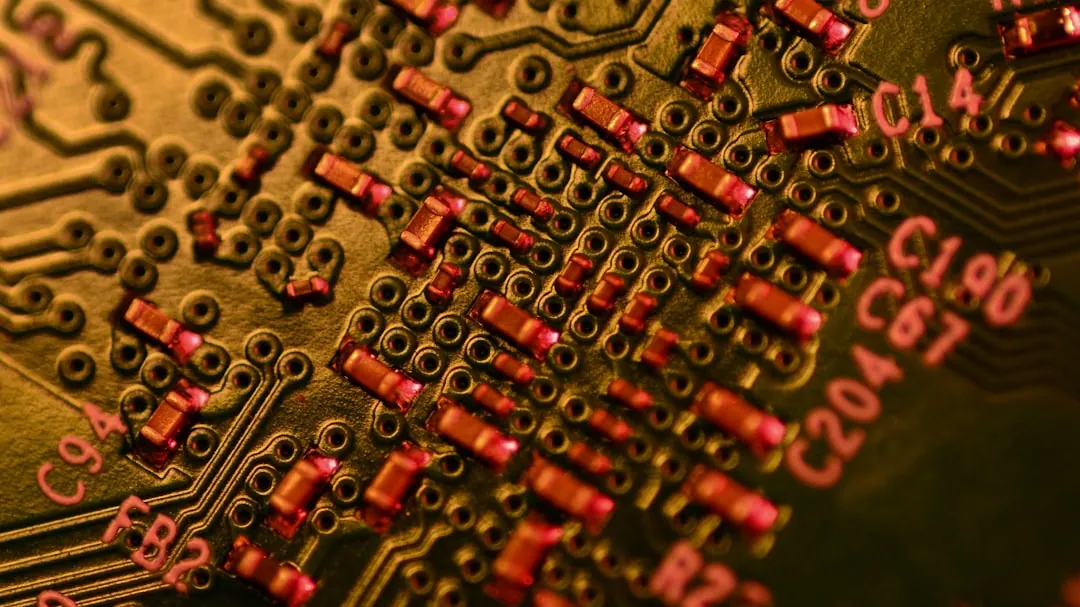

The company reports engagements with more than 30 semiconductor firms and ran a public demo with San Jose State University students producing RISC‑V cores from open‑source specs — useful for prototyping, but not equivalent to a confidential commercial tapeout on a modern process node. Cognichip has not yet disclosed completed customer chips or public production tapeouts.

Competitors and incumbents are also moving: Synopsys, Cadence, and Siemens EDA are adding AI features inside long‑standing toolchains, while startups such as ChipAgents and Ricursive pursue adjacent automation strategies. Cognichip’s differentiation claim is end‑to‑end automation that pushes several traditionally serial stages into concurrent, AI‑driven flows — a difference that only a successful foundry handoff and passing qualification tests will prove.

Concrete validation checkpoints and what to watch over the next 12–18 months

The clearest way to convert promise into industry adoption is a sequence of verifiable milestones: (1) completed tapeouts executed through a commercial foundry, (2) silicon that meets published reliability and performance metrics, and (3) independent customer reports quantifying cost and cycle time reductions. Cognichip’s stated targets are 75% lower design costs and 50% shorter timelines, but those figures need side‑by‑side comparison against typical EDA development runs on similar nodes.

| Claim or milestone | Required evidence | Who validates | Timing |

|---|---|---|---|

| Production tapeout | Foundry mask set, silicon wafer test reports | Foundry + customer test labs | Next 12–18 months (company target) |

| Performance & reliability parity | Published benchmarks, burn‑in and reliability data | Customer engineering teams, third‑party labs | After first production silicon |

| Cost/time reduction claims | Before/after project accounting, cycle‑time logs | Customers; auditors if requested | Within first commercial projects |

If Cognichip clears these checkpoints — particularly a foundry‑backed tapeout on advanced nodes the company plans to support (below 5 nm is explicitly on its hiring roadmap) — the industry will have concrete grounds to reassess how far AI can shift EDA workflows from serial, hand‑crafted sequences to concurrent automation.

Quick Q&A for engineering and procurement teams

Q: How soon should potential customers expect usable silicon?

A: The realistic horizon is the next 12–18 months for a validated production tapeout; any earlier timelines should be treated as preliminary until foundry and customer test reports are shared.

Q: Can a general LLM do this work?

A: Not without domain‑specific datasets, physics constraints, and guarded IP workflows; Cognichip emphasizes physics‑informed models and in‑place training to bridge that gap.

Q: What should procurement ask for in proofs?

A: Request foundry mask sets, silicon test reports, and before/after project accounting that maps claimed cost and time savings against comparable projects on the same process node.